# FMB121 Datasheet

Ver.1.0

Jul. 16, 2024

Flairmesh Technologies -1-

#### Copyright © 2024 Flairmesh Technologies

All rights reserved.

Flairmesh Technologies assumes no responsibility for any errors, which may appear in this document. Furthermore, Flairmesh Technologies reserves the right to alter the hardware, software, and/or specifications detailed herein at any time without notice, and do not make any commitment to update the information contained herein. Flairmesh Technologie's products are not authorized for use as critical components in life support devices or systems.

The *Bluetooth and Auracast* trademark is owned by the *Bluetooth* SIG Inc., USA. The aptX and cVc trademark is owned by Qualcomm Technologies International LTD. All other trademarks listed herein are owned by their respective owners.

Flairmesh Technologies -2-

#### **Release Record**

| Version | Release Date  | Comments           |

|---------|---------------|--------------------|

| 1.0     | Jul. 16, 2024 | The first release. |

|         |               |                    |

|         |               |                    |

|         |               |                    |

|         |               |                    |

|         |               |                    |

|         |               |                    |

Flairmesh Technologies -3-

# 1. Table of Contents

| 1  | Pinout and Description |           |                                               |    |  |

|----|------------------------|-----------|-----------------------------------------------|----|--|

|    | 1.1                    | Pin       | Assignments                                   | 7  |  |

|    | 1.2                    | Pin       | out Descriptions                              | 7  |  |

| 2  | Electri                | ical Chai | racteristics                                  | 9  |  |

|    | 2.1                    | Abs       | solute Maximum Rating                         | 9  |  |

|    | 2.2                    | Red       | commended Operating Conditions                | 10 |  |

|    | 2.3                    | Inpu      | ut/output Terminal Characteristics            | 10 |  |

|    | 2                      | .3.1      | Digital Terminals                             | 10 |  |

|    | 2                      | .3.2      | LED Driver Pads                               | 11 |  |

|    | 2                      | .3.3      | 10-bit Auxiliary ADC                          | 11 |  |

|    | 2                      | .3.4      | Class-D DAC Audio Output                      | 11 |  |

|    | 2                      | .3.5      | Class-AB DAC Audio Output                     | 12 |  |

|    | 2                      | .3.6      | High-quality (HQADC) Single-ended Audio Input | 13 |  |

|    | 2                      | 2.3.7     | High-quality (HQADC) Differential Audio Input | 13 |  |

|    | 2                      | .3.8      | Microphone Bias                               | 14 |  |

|    | 2                      | .3.9      | VBAT voltage measurement accuracy             | 14 |  |

|    | 2.4                    | Pov       | ver consumptions                              | 15 |  |

|    | 2.5                    | Ant       | enna Performance and Radiation Patters        | 15 |  |

| 3  | Physic                 | al Interf | faces                                         | 17 |  |

|    | 3.1                    | Pov       | ver Supply                                    | 17 |  |

|    | 3.2                    | Res       | set                                           | 17 |  |

|    | 3.3                    | Auc       | lio Interfaces                                | 18 |  |

|    | 3                      | 3.3.1     | Line/Mic inputs                               | 18 |  |

|    | 3                      | .3.2      | Line/Headphone Outputs                        | 18 |  |

|    | 3.4                    | Ger       | neral Purpose Analog IO                       | 19 |  |

|    | 3.5                    | LED       | Divers                                        | 19 |  |

|    | 3.6                    | Ser       | ial Interfaces                                | 19 |  |

|    | 3                      | .6.1      | UART                                          | 19 |  |

|    | 3                      | .6.2      | USB                                           | 19 |  |

|    | 3                      | 6.6.3     | I2C                                           | 20 |  |

|    | 3                      | .6.4      | SPI Interface                                 | 20 |  |

| 4  | Firmw                  | are Stac  | :k                                            | 20 |  |

| 5  | Refere                 | ence Des  | sign                                          | 21 |  |

| 6  | Mecha                  | anical Si | ze and Recommended PCB Footprint              | 22 |  |

| 7  | RF Lay                 | out Gui   | delines                                       | 23 |  |

| 8  | Reflov                 | v Profile |                                               | 24 |  |

| 9  | Packa                  | ge        |                                               | 25 |  |

| 10 | S                      | tatemer   | nt and Contact Information                    | 26 |  |

# 2. Table of Tables

| Table 1: Ordering Information                                    | 6  |

|------------------------------------------------------------------|----|

| Table 2: Pinout Definitions                                      | 9  |

| Table 3: Absolute Maximum Rating                                 | 9  |

| Table 4: Recommended Operating Conditions                        | 10 |

| Table 5: Digital Terminal                                        | 10 |

| Table 6: LED Driver Pads                                         | 11 |

| Table 7: LED Driver Pads                                         | 11 |

| Table 8: Class-D DAC Audio Output                                | 12 |

| Table 9: Class-AB DAC Audio Output                               | 13 |

| Table 10: High-quality Single Ended Audio Input                  | 13 |

| Table 11: Class-D DAC Audio Output                               | 14 |

| Table 12: Microphone Bias                                        | 14 |

| Table 13: VBAT Measurement Accuracy                              | 14 |

| Table 14: Power consumptions                                     | 15 |

| Table 15: Antenna Efficiencies and Gains                         | 15 |

| Table 16: Pin Status on Reset                                    | 17 |

| Table 17 : Headset Output Driver Modes                           | 19 |

| Table 18 : Possible UART Settings                                | 19 |

| Table of Figures                                                 |    |

| Table of Figures                                                 |    |

| Figure 1: Pinout of FMB121                                       | 7  |

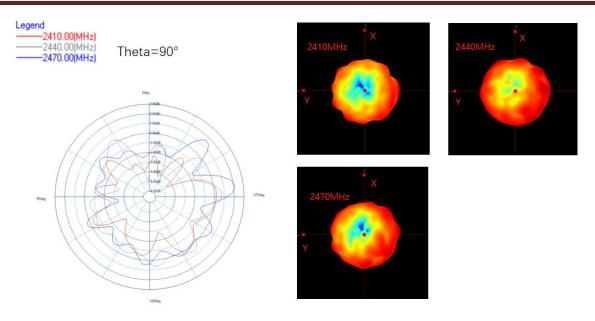

| Figure 2: Coordinate System Used in 3D Patterns                  | 16 |

| Figure 3: 3D Patterns – XZ Plane                                 |    |

| Figure 4: 3D Patterns – YZ Plane                                 | 16 |

| Figure 5: 3D Patterns – XY Plane                                 |    |

| Figure 6: FMB121 Stacks                                          | 20 |

| Figure 7: Reference Design                                       | 21 |

| Figure 8: Mechanical Size and Recommended PCB Footprint          | 22 |

| Figure 9 : Placement the module and the ground of main PCB Board |    |

| Figure 10: Typical Lead-Free Re-flow Solder Profile for FMB121   | 24 |

| Figure 11: FMB121 Plastic Tray Package                           | 25 |

#### **Description:**

FMB121 is a dual-mode Class 1 Bluetooth® V5.4 module, offering robust support for both classic Bluetooth profiles (A2DP/HSP/HFP) and the latest low energy audio standards TMAP and PBP in a single unit. Powered by internal multi-core processors, it efficiently handles all required audio codecs and profiles. The module features an integrated PCB antenna, stereo audio output, and a single analog MIC input, all packed into a compact castellated hole footprint. This makes it an ideal System-on-Chip (SoC) Bluetooth solution for headsets and speakers. In addition to standard SBC and LC3 decoders for A2DP and LE audio respectively, FMB121 supports advanced audio codecs such as aptX®, aptX HD, and aptX adaptive, ensuring high-fidelity music streaming. It includes a super low latency mode for enhanced gaming gaming experiences.

With an ASCII command-based control interface accessible via UART, FMB121 simplifies integration of Bluetooth audio functionality into host systems, requiring minimal effort from developers.

Typical Bluetooth & LE audio applications:

- Bluetooth audio speaker

- Auracast® receiver

- Home entertainment equipment

#### Features:

- Dual mode Bluetooth® v5.4

- Support BLE 2M PHY

- +15dBm BR TX power, -97dBm BR RX sensitivity

- +15dBm BLE TX power, -100.5dBm BLE 1Mb/s RX sensitivity

- PCB antenna with 2.7dBi gain

- Supported profiles: TMAP (CT, UMR, BMR), PBP (PBK, Auracast®), A2DP (SNK), AVRCP (TG/CT).

- Profiles supported with customized firmware: HFP, HID, SPP, OPP etc.

- UART/I2C/SPI master multiplexed with PIOs

- 11 digital PIOs, 2 LED outputs multiplexed with AIOs

- SBC, aptX, aptX HD, aptX adaptive and lossless decoder and LC3 encoder/decoder

- 22mm x 12mm x 2.2mm

- Weight: approximately 1g

- Plated half-holes SMT pads for easy and reliable PCB mounting

- Bluetooth QDID:

- FCC ID:

- CE

- RCM

- RoHS compliant

| Ordering Number | Package      | Items in One Package | Comments |

|-----------------|--------------|----------------------|----------|

| FMB121-P        | Plastic tray | 80                   |          |

| FMB121-T        | Tape         | TBD                  |          |

Table 1: Ordering Information

Please also supply the customer firmware code issued by Flairmesh Technologies when you place the order.

Flairmesh Technologies -6-

# 1 Pinout and Description

## 1.1 Pin Assignments

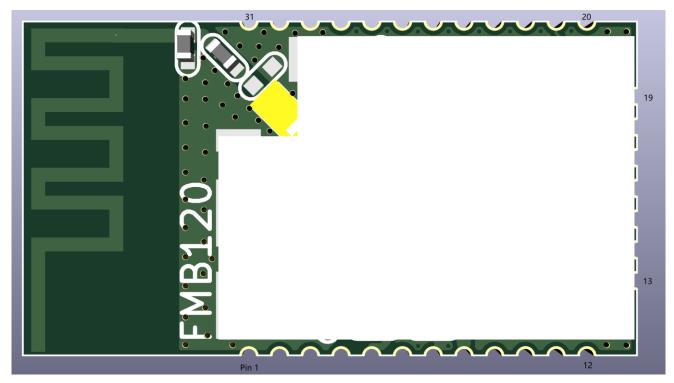

Figure 1: Pinout of FMB121

## 1.2 Pinout Descriptions

| Pin | Symbol       | I/O Type                                                                   | Description                                                                                                                                                                                                                                                                                               |

|-----|--------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND          | Ground                                                                     | Ground                                                                                                                                                                                                                                                                                                    |

| 2   | 3V3/VBAT     | Power input                                                                | Battery voltage input                                                                                                                                                                                                                                                                                     |

| 3   | PIO0/VREG_EN | Digital input                                                              | Typically connected to an ON/OFF push button. If power is present from the battery and/or charger, and software has placed the device in the OFF or DORMANT state, a button press boots the device. Also usable as a digital input in normal operation. No pull.  Additional function:  PIO[0] input only |

| 4   | PIO8         | Digital bidirectional with programable strength internal pull-up/pull-down | Programmable IO 8, weak pull down when reset                                                                                                                                                                                                                                                              |

Flairmesh Technologies -7-

|   |    |               |                                                                            | TMD121 Datasheet Vel.1                                                                                                                                                |

|---|----|---------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5  | VDD_IO        | Power input                                                                | PIO supply, 1.8V or 3.3V, needs to be powered at the same time as VBAT or VBUS                                                                                        |

|   | 6  | 1V8_OUT       | Power output                                                               | Can provide 100mA for external circuits                                                                                                                               |

| - | 7  | GND           | Ground                                                                     | Ground                                                                                                                                                                |

| - | 8  | VBUS          | Power input                                                                | 5V input                                                                                                                                                              |

| - | 9  | PIO1/RESETB   | Digital bidirectional with programable strength internal pull-up/pull-down | Automatically defaults to RESET# mode when the device is unpowered, or in off modes. Reconfigurable as a PIO after boot. Programmable IO 1, strong pull-up when reset |

|   | 10 | PIO2          | Digital bidirectional with programable strength internal pull-up/pull-down | Programmable IO 2, weak pull down when reset                                                                                                                          |

|   | 11 | USB_DP        | Digital                                                                    | USB Full Speed device D- I/O. IEC-<br>61000-4-2 (device level) ESD<br>Protection                                                                                      |

| - | 12 | USB_DN        | Digital                                                                    | USB Full Speed device D- I/O. IEC-61000-4-2 (device level) ESD Protection                                                                                             |

|   | 13 | PIO4          | Analog or digital input/open drain output                                  | Programmable IO 4, weak pull down when reset                                                                                                                          |

|   | 14 | AIO1/LED1     | Analog or digital input/open drain output                                  | General purpose analog/digital input or open drain LED output 1                                                                                                       |

|   | 15 | AIO0/LED0     | Analog or digital input/open drain output                                  | General purpose analog/digital input or open drain LED output 0                                                                                                       |

|   | 16 | PIO34         | Digital bidirectional with programable strength internal pull-up/pull-down | Programmable IO 34, weak pull-<br>down when reset                                                                                                                     |

|   | 17 | PIO21         | Digital bidirectional with programable strength internal pull-up/pull-down | Programmable IO 21, weak pull-<br>down when reset                                                                                                                     |

|   | 18 | PIO36         | Digital bidirectional with programable strength internal pull-up/pull-down | Programmable IO 36, strong pull-up when reset                                                                                                                         |

|   | 19 | PIO7          | Digital bidirectional with programable strength internal pull-up/pull-down | Programmable IO 7, strong pull-up when reset                                                                                                                          |

|   | 20 | PIO5/UART_RX  | Digital bidirectional with programable strength internal pull-up/pull-down | Programmable IO 5, weak pull down when resetting, Additional function:  UART RX                                                                                       |

|   | 21 | PIO15/UART_TX | Digital bidirectional with programable strength internal pull-up/pull-down | Programmable IO 15, strong pull-up when reset,                                                                                                                        |

|   |    |               | ·                                                                          | · · · · · · · · · · · · · · · · · · ·                                                                                                                                 |

Flairmesh Technologies -8-

|    |          |                   | Additional function:                                          |

|----|----------|-------------------|---------------------------------------------------------------|

|    |          |                   | ■ UART TX                                                     |

| 22 | SPK_LN   | Analog            | Headphone/speaker left channel differential output, negative  |

| 23 | SPK_LP   | Not connected     | Headphone/speaker left channel differential output, positive  |

| 24 | MIC_BIAS | Mic bias output   | Mic bias output                                               |

| 25 | MIC2_N   | Analog            | Microphone differential 2 input, negative                     |

| 26 | MIC2_P   | Analog            | Microphone differential 2 input, positive                     |

| 27 | SPK_RP   | Analog            | Headphone/speaker right channel differential output, positive |

| 28 | SPK_RN   | Analog            | Headphone/speaker right channel differential output, negative |

| 29 | MIC_GND  | Microphone ground | Ground of microphone                                          |

| 30 | GND      | Ground            | Ground                                                        |

| 31 | GND      | Ground            | Ground                                                        |

Table 2: Pinout Definitions

# **2 Electrical Characteristics**

## 2.1 Absolute Maximum Rating

| Rating                | Min  | Max  | Unit |

|-----------------------|------|------|------|

| Storage Temperature   | -40  | +85  | °C   |

| VBUS Voltage          | -0.4 | 6.5  | V    |

| USB_DP/USB_DN Voltage | -0.4 | 3.8  | V    |

| VBAT Voltage          | -0.4 | 4.8  | V    |

| PIO Voltage           | -0.4 | 3.6  | V    |

| LED Voltage           | -0.4 | 6.5  | V    |

| AIO Voltage           | -0.4 | 1.95 | V    |

| MIC Voltage           | -0.4 | 2.1  | V    |

Table 3: Absolute Maximum Rating

Flairmesh Technologies -9-

## 2.2 Recommended Operating Conditions

| Operating Condition          | Min  | Тур | Max  | Unit |

|------------------------------|------|-----|------|------|

| Operating Temperature Range* | -40  |     | +85  | °C   |

| VBUS                         | 4.75 | 5.0 | 6.5  | V    |

| USB_DP/USB_DN Voltage        | 0    |     | 3.6  | V    |

| VBAT Voltage                 | 3.0  | 3.7 | 4.6  | V    |

| PIO Voltage                  | 1.7  | 3.3 | 3.6  | V    |

| LED voltage                  | 0    |     | 6.5  | V    |

| AIO Voltage                  | 0    |     | 1.95 | V    |

Table 4: Recommended Operating Conditions

Note \*: Charger operates in a range from -10 to +85 (not including battery).

## 2.3 Input/output Terminal Characteristics

## 2.3.1 Digital Terminals

| Supply Voltage Levels                                       | Min                | Тур  | Max               | Unit                |  |  |

|-------------------------------------------------------------|--------------------|------|-------------------|---------------------|--|--|

| Input Voltage Levels                                        |                    |      |                   |                     |  |  |

| V <sub>IL</sub> input logic level low                       | 0                  | -    | 0.25 x<br>VDD_PIO | V                   |  |  |

| V <sub>IH</sub> input logic level high                      | 0.625 x<br>VDD_PIO | -    | -                 | V                   |  |  |

| Drive current (configurable 2,4,8,12mA)                     | 2                  | 4    | 12                | mA                  |  |  |

| Output Voltage Levels                                       |                    |      |                   |                     |  |  |

| V <sub>OL</sub> output logic level low, at max rated drive  | -                  | -    | 0.22 x<br>VDD_PIO | V                   |  |  |

| V <sub>OH</sub> output logic level high, at max rated drive | 0.75 x<br>VDD_PIO  | -    | -                 | V                   |  |  |

| Pull Strength                                               |                    |      |                   |                     |  |  |

| Strong pull-up/down                                         | 50                 | 70   | 125               | $\mathbf{k} \Omega$ |  |  |

| Weak pull-up/down                                           | 729                | 1050 | 1350              | $\mathbf{k}\Omega$  |  |  |

Table 5: Digital Terminal

Flairmesh Technologies -10-

#### 2.3.2 LED Driver Pads

| LED driver pads                        |                      | Min | Тур | Max | Unit |

|----------------------------------------|----------------------|-----|-----|-----|------|

| Open drain current                     | High impedance state | -   | -   | 5   | uA   |

| Open drain current                     | Current sink state   | -   | -   | 50  | mA   |

| LED pad resistance                     | V < 0.5V             | -   | -   | 12  | Ω    |

| V <sub>IL</sub> input logic level low  |                      | -   | -   | 0.4 | V    |

| V <sub>IH</sub> input logic level high |                      | 0.8 | -   | -   | V    |

Table 6: LED Driver Pads

## 2.3.3 10-bit Auxiliary ADC

| 10-bit auxiliary ADC           | ,                     | Min   | Тур   | Max                              | Unit |

|--------------------------------|-----------------------|-------|-------|----------------------------------|------|

| Resolution                     |                       | -     | -     | 10                               | Bits |

| Internal voltage reference     | ce                    | 1.746 | 1.800 | 1.854                            | V    |

| Functional input voltage range |                       | 0     | -     | Internal<br>voltage<br>reference | V    |

| Accuracy (Guaranteed           | INL                   | -3    | -     | 3                                | LSB  |

| monotonic)                     | DNL                   | -1    | -     | 2                                | LSB  |

| Offset                         |                       | -1    | -     | 1                                | LSB  |

| Gain error                     |                       | -1    | -     | 1                                | %    |

| Hardware conversion time       |                       | -     | 10    | -                                | μs   |

| LED pad leakage                |                       | -1    | -     | 1                                | uA   |

| External pad capacitano        | e for < 0.5 LSB error | 0     | 40    | -                                | nF   |

Table 7: LED Driver Pads

## 2.3.4 Class-D DAC Audio Output

| Parameter                              | Conditions                              | Min | Тур | Max | Unit |

|----------------------------------------|-----------------------------------------|-----|-----|-----|------|

| Input Sample Width                     | -                                       | -   | -   | 24  | Bits |

| Input Sample Rate, F <sub>sample</sub> | -                                       | 8   | -   | 96  | kHz  |

| Output Power                           | 0 dBFS, 32 Ω load<br>-3 dBFS, 16 Ω load | -   | -   | 30  | mW   |

| Load                                   | -                                       | 16  | 32  | 30k | Ω    |

Flairmesh Technologies -11-

| SNR       | $F_{in}$ =1kHz<br>$48$ kHz $F_{sample}$<br>Input amplitude = 0 dBFS<br>Analog gain = 0 dB<br>B/W=20Hz->20kHz<br>A-Weighted<br>$32 \Omega load$ | - | 105.1 | - | dB    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|---|-------|

| THD+N     | $F_{in}$ =1kHz<br>$48$ kHz $F_{sample}$<br>Input amplitude = 0 dBFS<br>Analog gain = 0 dB<br>B/W=20Hz->20kHz<br>$32 \Omega load$               | - | -88.1 | - | dB    |

| RMS noise | 48kHz F <sub>sample</sub> Input amplitude = -200 dBFS Analog gain = 0 dB B/W=20Hz->20kHz A-Weighted 32 Ω load                                  | - | 5.50  | - | uVrms |

Table 8: Class-D DAC Audio Output

## 2.3.5 Class-AB DAC Audio Output

| Parameter                                 | Condition                                          | ons                  | Min | Тур   | Max | Unit |

|-------------------------------------------|----------------------------------------------------|----------------------|-----|-------|-----|------|

| Input Sample Width                        | -                                                  |                      | -   | -     | 24  | Bits |

| Input Sample Rate,<br>F <sub>sample</sub> | -                                                  |                      | 8   | -     | 96  | kHz  |

| Output Power                              | 0 dBFS, 32 $\Omega$ load -3 dBFS, 16 $\Omega$ load |                      | -   | -     | 30  | mW   |

| Load                                      | -                                                  |                      | 16  | 32    | 30k | Ω    |

|                                           | F <sub>in</sub> =1kHz<br>48kHz F <sub>sample</sub> | Analog gain = 0 dB   |     | 104.7 |     |      |

|                                           | Input amplitude = 0 dBFS                           | Analog gain = -6 dB  |     | 103.8 |     |      |

| SNR                                       | B/W=20Hz->20kHz<br>A-Weighted<br>32 Ω load         | Analog gain = -12 dB | -   | 100.2 | -   | dB   |

|                                           | Quiet mode                                         | Analog gain = 0 dB   |     | 120.0 |     |      |

Flairmesh Technologies -12-

|                               | F <sub>in</sub> =1kHz<br>48kHz F <sub>sample</sub> | Analog gain = 0 dB   |    | -93.3 |   |       |

|-------------------------------|----------------------------------------------------|----------------------|----|-------|---|-------|

| THD+N                         | IHD+N                                              | Analog gain = -3 dB  | -  | -92.5 | - | dB    |

|                               | B/W=20Hz->20kHz<br>32 Ω load                       | Analog gain = -6 dB  |    | -91.9 |   |       |

|                               | 48kHz F <sub>sample</sub> Input amplitude = -      | Analog gain = 0 dB   |    | 5.77  |   |       |

| RMS noise                     | 200 dBFS<br>B/W=20Hz->20kHz                        | Analog gain = -6 dB  |    | 3.23  |   | N     |

| KIVIS HOISE                   | A-Weighted<br>32 Ω load                            | Analog gain = -12 dB | _  | 2.44  | _ | uVrms |

|                               | Quiet mode                                         | Analog gain = 0 dB   |    | <1    |   |       |

| Stereo separation (crosstalk) | -                                                  |                      | 80 | -     | - | dB    |

Table 9: Class-AB DAC Audio Output

## 2.3.6 High-quality (HQADC) Single-ended Audio Input

| Parameter                                  | Conditions                                                                                                           | Min | Тур   | Max | Unit    |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-------|-----|---------|

| Output Sample Width                        | -                                                                                                                    | -   | -     | 24  | Bits    |

| Output Sample Rate,<br>F <sub>sample</sub> | -                                                                                                                    | 8   | -     | 96  | kHz     |

| Input level                                | -                                                                                                                    | -   | -     | 2.4 | V pk-pk |

| Innut impedance                            | 0dB to 24dB analog gain                                                                                              | -   | 20    | -   | kΩ      |

| Input impedance                            | 27dB to 39dB analog gain                                                                                             | -   | 10    | -   | kΩ      |

| Signal to Noise Ratio, SNR                 | F <sub>in</sub> =1kHz 48kHz F <sub>sample</sub> B/W=20Hz->20kHz A- Weighted THD+N < 0.1% 2.4V pk-pk input (0dB gain) | -   | 99.4  | -   | dBA     |

| THD+N                                      | F <sub>in</sub> =1kHz 48kHz 2.4V pk-pk input (0dB gain)                                                              | -   | -91.9 | -   | dB      |

| Analog Gain                                | 3dB Steps                                                                                                            | 0   | -     | 39  | dB      |

Table 10: High-quality Single Ended Audio Input

## 2.3.7 High-quality (HQADC) Differential Audio Input

| Parameter | Conditions | Min | Тур | Max | Unit |

|-----------|------------|-----|-----|-----|------|

|-----------|------------|-----|-----|-----|------|

Flairmesh Technologies -13-

| Output Sample Width                        | -                                                                                                                    | - | -     | 24  | Bits    |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---|-------|-----|---------|

| Output Sample Rate,<br>F <sub>sample</sub> | -                                                                                                                    | 8 | -     | 96  | kHz     |

| Input level                                | -                                                                                                                    | - | -     | 2.4 | V pk-pk |

| lanut impadance                            | 0dB to 24dB analog gain                                                                                              | - | 20    | -   | kΩ      |

| Input impedance                            | 27dB to 39dB analog gain                                                                                             | - | 10    | -   | kΩ      |

| Signal to Noise Ratio, SNR                 | F <sub>in</sub> =1kHz 48kHz F <sub>sample</sub> B/W=20Hz->20kHz A- Weighted THD+N < 0.1% 2.4V pk-pk input (0dB gain) | - | 99    | -   | dBA     |

| THD+N                                      | F <sub>in</sub> =1kHz 48kHz 2.4V pk-pk input (0dB gain)                                                              | - | -94.9 | -   | dB      |

| Analog Gain                                | 3dB Steps                                                                                                            | 0 | -     | 39  | dB      |

Table 11: Class-D DAC Audio Output

## 2.3.8 Microphone Bias

| Parameter                             | Conditions                             | Min  | Тур | Max  | Unit  |

|---------------------------------------|----------------------------------------|------|-----|------|-------|

| Output voltage (Tunable, step = 0.1V) | -                                      | 1.5  | -   | 2.1  | V     |

| Output current capability             | -                                      | 0.07 | -   | 6.00 | mA    |

| DC accuracy                           | -                                      | -60  | -   | 60   | mV    |

| Output noise                          | B/W=20Hz->20kHz<br>Unweighted          | 4.5  | 5.1 | 7.3  | uVrms |

| Crosstalk between microphones         | Using recommended application circuit  | -    | 80  | -    | dB    |

| Load capacitance                      | From parasitic PCB routing and package | -    | -   | 0.1  | nF    |

Table 12: Microphone Bias

## 2.3.9 VBAT voltage measurement accuracy

| Measurement                       | Min | Тур  | Max    | Unit |

|-----------------------------------|-----|------|--------|------|

| VBAT voltage measurement accuracy | -   | +/-1 | +/-1.5 | %    |

Table 13: VBAT Measurement Accuracy

Flairmesh Technologies -14-

## 2.4 Power consumptions

| Operating Condition                                                             | Typical | Unit |

|---------------------------------------------------------------------------------|---------|------|

| Dormant                                                                         | 23      | uA   |

| Deep sleep, idle                                                                | -       | uA   |

| Connected, 495ms BT Sniff sub-rating                                            | -       | uA   |

| Connected, 187ms BT Sniff, 2 links, four slots no retry, AFH on                 | -       | mA   |

| Connected, 11.25ms BT Sniff                                                     | -       | mA   |

| Connected with audio streaming (A2DP), SBC in 192 kbit, SBC Out 192kbit, Output |         |      |

| Mono LP_DAC 48 KHz                                                              | -       | mA   |

Table 14: Power consumptions

#### Note:

Power consumption depends on the firmware used. Typical values are shown in the table.

Sniff mode ---- In Sniff mode, the duty cycle of the slave's activity in the piconet may be reduced. If a slave is in active mode on an ACL logical transport, it shall listen in every ACL slot to the master traffic, unless that link is being treated as a scatternet link or is absent due to hold mode. With sniff mode, the time slots when a slave is listening are reduced, so it benefits the power consumption of the slave and the master shall only transmit to a slave in specified time slots. The sniff anchor points are spaced regularly with an interval of Tsniff, which depends on the firmware used.

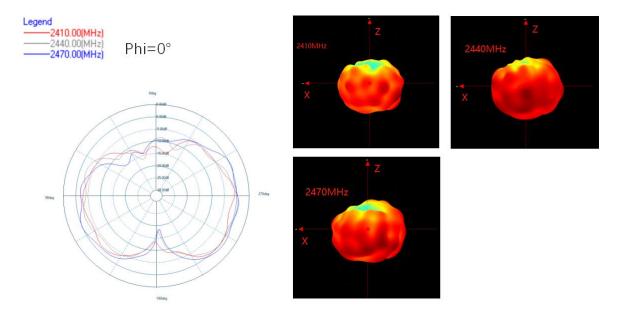

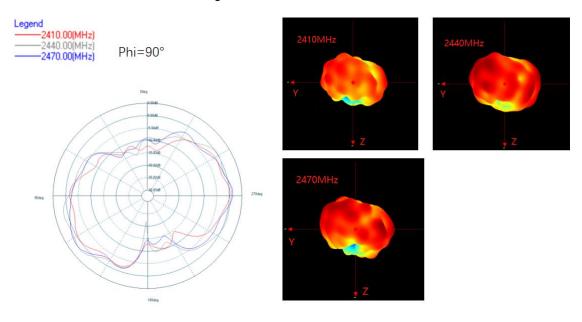

#### 2.5 Antenna Performance and Radiation Patters

Antenna performance measured from the evaluation board.

| Frequency (MHz) | Efficiency % | Efficiency dB | Gain dB |

|-----------------|--------------|---------------|---------|

| 2400            | 40%          | -4.0          | 1.1     |

| 2410            | 45%          | -3.4          | 2.2     |

| 2420            | 52%          | -2.9          | 2.2     |

| 2430            | 55%          | -2.6          | 2.0     |

| 2440            | 56%          | -2.5          | 2.1     |

| 2450            | 53%          | -2.8          | 1.4     |

| 2460            | 61%          | -2.2          | 2.7     |

| 2470            | 61%          | -2.2          | 2.1     |

| 2480            | 60%          | -2.2          | 2.7     |

| 2490            | 58%          | -2.4          | 2.1     |

| 2500            | 57%          | -2.4          | 2.3     |

Table 15: Antenna Efficiencies and Gains

Flairmesh Technologies -15-

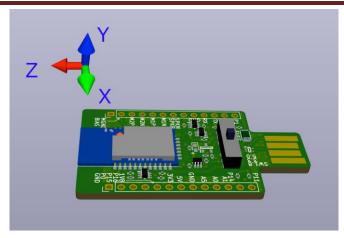

Figure 2: Coordinate System Used in 3D Patterns

Figure 3: 3D Patterns - XZ Plane

Figure 4: 3D Patterns – YZ Plane

Flairmesh Technologies -16-

Figure 5: 3D Patterns - XY Plane

# 3 Physical Interfaces

## 3.1 Power Supply

There are three power supply schemes available for the module. It can be powered by a Li-poly battery (3.7V), a 3.3V DC on its VBAT or a 5V DC on its VBUS. Please refer to the reference designs in 5.

#### 3.2 Reset

The module may be reset from several sources: RESETB pin, power-on reset, USB charger attach reset and software configured watchdog timer.

The RSTB pin is an active low reset. It is recommended that RSTB be applied for a period greater than  $120\mu s$ .

At reset the digital I/O pins are set to inputs for bi-directional pins and outputs are tri-state. The pull-down state is shown below.

| Pin Name / Group   | Pin Status on Reset |

|--------------------|---------------------|

| USB_DP             | Tristate            |

| USB_DN             | Tristate            |

| PIO0               | No Pull             |

| PIO[1,7,15,36]     | PUS                 |

| PIO[2,4,5,8,21,34] | PDW                 |

Table 16: Pin Status on Reset

Note: PUS - Strong pull-up, PDS - Strong pull-down, PUW - Weak pull-up, PDW - Weak pull-down.

If RSTB is held low for > 1.8 s and VBUS is not applied, the module turns off. A rising edge on PIO0 or VBUS is then required to power on.

Flairmesh Technologies -17-

#### 3.3 Audio Interfaces

#### 3.3.1 Line/Mic inputs

The module has one high-quality audio input ADC (HQADC). They are also suitable for supporting mixed differential and single-ended applications. The ADC is 24-bit, and capable of sample rates from 8 kHz to 96 kHz.

Inputs should be AC coupled, typically using a  $2.2~\mu F$  capacitor. Reducing this capacitor value, reduces low-frequency response attenuation.

The ADC channel receives a differential/single-ended input and generates a 3-bit Delta-Sigma modulated output that goes into a decimator. The ADC serves both line and mic modes.

The input is fed into a programmable gain amplifier. The audio output from the pre-amplifier stage is always differential and has a maximum amplitude of 2.4 Vpp (peak-to-peak). The pre-amplifier can support single ended and differential inputs at the same input amplitude. At 0 dB gain the maximum input is 2.4 Vpp.

If the audio signal is single-ended, the input goes approximately 300 mV below ground and approximately 300 mV above the 1.8 V audio power supply rail.

The module has a microphone bias source for supplying electret or MEMS microphones, with an output voltage configurable from 1.5V to 2.1V, capable of biasing an external analog microphones at a load current of up to 6 mA.

### 3.3.2 Line/Headphone Outputs

Two high-quality audio output DACs (HQDAC) drive stereo low impedance differential loads (bridge-tied load (BTL)headphones) or Line out.

The HQ-DACs support two modes of operation. Class-D is a high efficiency, switching mode amplifier. The secondary Class-AB is a linear amplifier and consumes more power.

| Mode     | Description                                                           |  |  |

|----------|-----------------------------------------------------------------------|--|--|

| Class-D  | Enables a lower power consumption for the headset.                    |  |  |

|          | 3-state BD modulation enables a filter-free configuration.            |  |  |

|          | Directly driven from the digital circuitry.                           |  |  |

|          | Most of the analog portion is powered-down.                           |  |  |

|          | Drives differential headphone loads of 16 $\Omega/32~\Omega$ .        |  |  |

| Class-AB | Enables either headphone or speaker applications.                     |  |  |

|          | Can drive the same headphone outputs instead of switching to Class-D. |  |  |

Flairmesh Technologies -18-

| Typically, useful for driving high impedance loads such as differential line |  |

|------------------------------------------------------------------------------|--|

| out, or analog input power amp.                                              |  |

| Additional external filtering may be required for line out applications that |  |

| drive an active component such as a power amplifier.                         |  |

Table 17: Headset Output Driver Modes

#### 3.4 General Purpose Analog IO

The module has two general-purpose analogue interface pins multiplexed with LED pads. In a Li-poly battery application, the VBAT pin can measure the battery voltage directly.

#### 3.5 LED Drivers

The FMB121 includes PWM LED driver for driving LEDs. There are 2 open-drain LED outputs multiplexed with AIOs. Any PIOs can also be mapped into LED output by firmware.

#### 3.6 Serial Interfaces

#### 3.6.1 **UART**

The module has a standard UART serial interface that provides a simple mechanism for communicating using RS232 protocol.

| Parameter           |         | Possible Values       |

|---------------------|---------|-----------------------|

| Baud Rate           | Minimum | 2400 baud (≤2%Error)  |

|                     |         | 19200 baud (≤1%Error) |

|                     | Maximum | 4M baud (≤1%Error)    |

| Flow control        |         | RTS/CTS or None       |

| Parity              |         | None, Odd or Even     |

| Number of Stop Bits |         | 1 or 2                |

| Bits per Byte       |         | 8                     |

Table 18: Possible UART Settings

#### 3.6.2 USB

FMB121 has a full-speed (12 Mbps) USB port and enumerates as a compound device with a hub. The enabled audio source/sink/HID/CDC device appears behind that hub.

The DP 1.5k pull-up is integrated internally. No series resistors are required on the USB data lines.

The VBUS input is tolerant of a constant 6.5V and transients up to 7.0V. Use an external clamping protection device if extra overvoltage protection is required.

Flairmesh Technologies -19-

FMB121 supports charger detection to the USB BC 1.2 specification.

It provides Data Contact Detection (DCD) using an internal current source, and provides:

- Detection of Standard Downstream Ports (SDP)

- Charging Downstream Ports (CDP)

- Dedicated Downstream Ports (DCP)

The 10-bit auxiliary ADC reads the voltage on the USB data lines. This enables detection of proprietary chargers that bias the voltage on the USB data lines.

For USB Type-C® connectors, use the LED pins to detect the voltage on the USB Configuration Channel (CC) line pins (CC1 and CC2) to detect the charge current capabilities of the upstream device.

#### 3.6.3 I2C

Any two PIOs can be used to form a master I2C interface.

#### 3.6.4 SPI Interface

Any four PIOs can be used to form a SPI interface. Firmware can be customized to connect with variable peripherals.

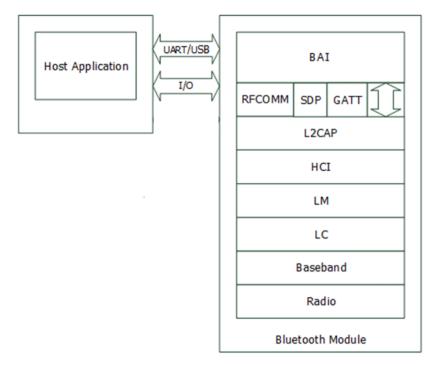

## 4 Firmware Stack

Figure 6: FMB121 Stacks

FMB121 is supplied with qualified Bluetooth 5.4 stack firmware. With Flairmesh's BAI interface, the host MCU can easily controls A2DP (SNK role), AVRCP (TG/CT role), HFP (handsfree role), TMAP (CT, UMR and BMR role), PBP (PBK role), SPP (A and B), OPP (client), HID (peripheral) profiles running on the module.

Flairmesh Technologies -20-

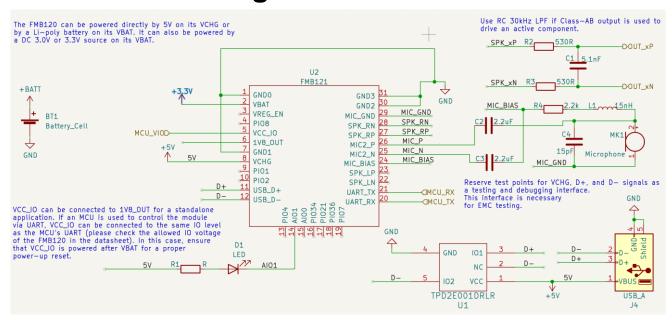

# **5 Reference Design**

Figure 7: Reference Design

Flairmesh Technologies -21-

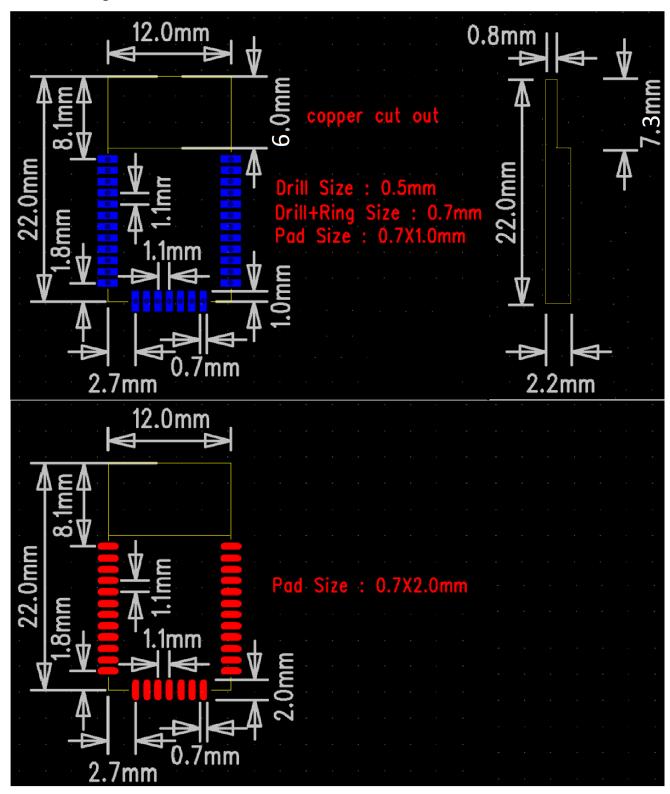

# 6 Mechanical Size and Recommended PCB Footprint

Figure 8: Mechanical Size and Recommended PCB Footprint

Flairmesh Technologies -22-

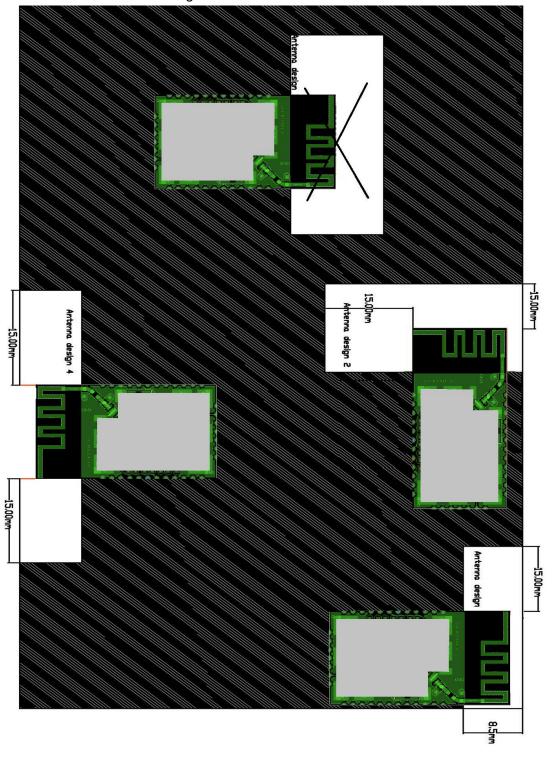

# 7 RF Layout Guidelines

FMB121 integrates an on-board Meander line antenna to radiate and receive the RF signals. The antenna has been well designed and tuned for common usage but it still needs to have good ground clearance around the antenna to get good RF performance.

- 1. No ground below antenna region (copper cut out in Figure 8) of the FMB121.

- 2. There should also have a good ground panel and clearance on the main PCB board on which the module is mounted. As shown in Figure 9.

Figure 9: Placement the module and the ground of main PCB Board

Flairmesh Technologies -23-

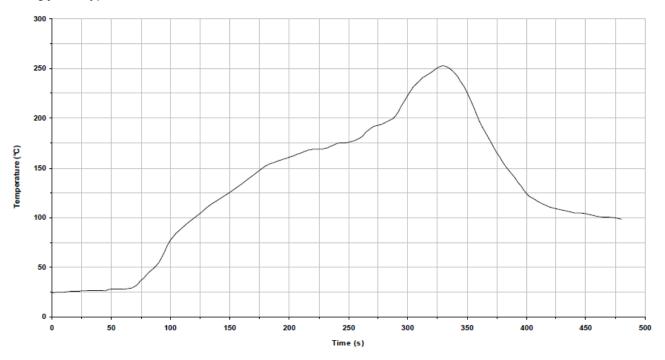

## 8 Reflow Profile

FMB121 is compatible with industrial standard reflow profile for Pb-free solders. The soldering profile depends on various parameters necessitating a set up for each application. The data here is given only for guidance on solder re-flow.

There are four zones:

Preheat Zone - This zone raises the temperature at a controlled rate, typically 1-2.5°C/s.

Equilibrium Zone - This zone brings the board to a uniform temperature and also activates the flux. The duration in this zone (typically 2-3 minutes) will need to be adjusted to optimise the out gassing of the flux. Reflow Zone- The peak temperature should be high enough to achieve good wetting but not so high as to cause component discoloration or damage. Excessive soldering time can lead to intermetallic growth which can result in a brittle joint.

Cooling Zone - The cooling rate should be fast, to keep the solder grains small which will give a longer lasting joint. Typical rates will be 2-5°C/s.

Figure 10: Typical Lead-Free Re-flow Solder Profile for FMB121

Key features of the profile:

- Initial Ramp = 1-2.5°C/sec to 175°C ±25°C equilibrium

- Equilibrium time = 60 to 180 seconds

- Ramp to Maximum temperature (250°C) = 3°C/sec max.

- Time above liquidus temperature (217°C): 45-90 seconds

- Device absolute maximum reflow temperature: 255°C

Note: Customer might choose a local 0.2mm thickness solder cream for the module, or use 0.15mm to match other components in the same PCB.

Flairmesh Technologies -24-

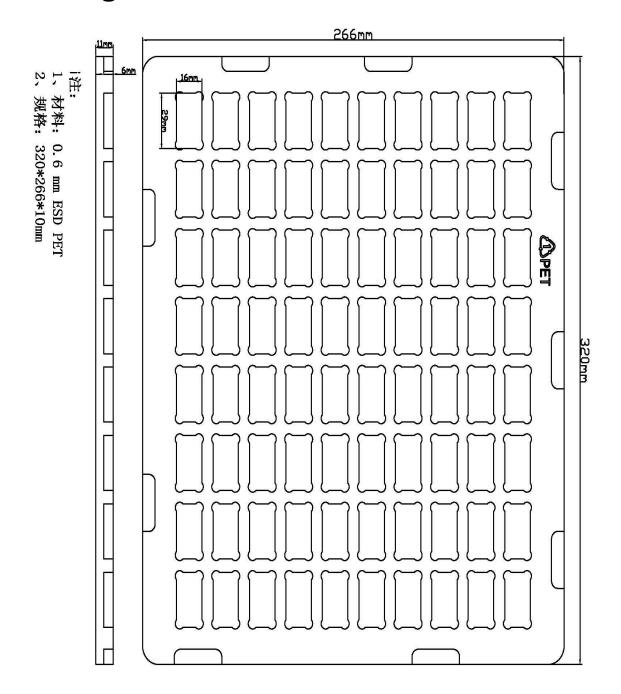

# 9 Package

Figure 11: FMB121 Plastic Tray Package

Plastic tray, plus aluminum bags do vacuum packing. Items in One Package number of 80 PCS, external aluminum foil vacuum packaging.

The module's Moisture Sensitivity Level is level 3 in accordance with JEDEC J-STD-020.

Flairmesh Technologies -25-

## 10 Statement and Contact Information

Radioworks Microelectronics PTY LTD is the business name holder of Flairmesh Technologies.

#### FCC statements:

This device complies with part 15 of the FCC rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

NOTE: The manufacturer is not responsible for any radio or TV interference caused by unauthorized modifications or changes to this equipment. Such modifications or changes could void the user's authority to operate the equipment.

NOTE: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- -Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- -Consult the dealer or an experienced radio/TV technician for help.

Federal Communication Commission (FCC) Radiation Exposure Statement

When using the product, maintain a distance of 20cm from the body to ensure compliance with RF exposure requirements.

This device is intended only for OEM integrators under the following conditions: 1. The antenna must be installed such that 20 cm is maintained between the antenna and users. 2. The transmitter module may not be colocated with any other transmitter or antenna. As long as the two conditions above are met, additional transmitter testing will not be required. However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required for the installed module.

**Important Note:** In the event that these conditions cannot be met (for example certain laptop configurations or co-location with another transmitter), then the Federal Communications Commission of the U.S. Government (FCC) and the Canadian Government authorizations are no longer considered valid and the FCC ID cannot be used on the final product. In these circumstances, the OEM integrator shall be responsible for re-evaluating the end-product (including the transmitter)

and obtaining a separate FCC authorization in the U.S.

**OEM Integrators - End Product Labeling Considerations:** This transmitter module is authorized only for use in device where the antenna may be installed such that 20 cm may be maintained between the antenna and users.

Flairmesh Technologies -26-

The final end product must be labeled in a visible area with the following: "Contains, FCC ID: 2A22WFMB121". The grantee's FCC ID can be used only when all FCC compliance requirements are met.

**OEM Integrators - End Product Manual Provided to the End User:** The OEM integrator shall not provide information to the end user regarding how to install or remove this RF module in end product user manual. The end user manual must include all required regulatory information and warnings as outlined in this document.

Appropriate measurements (e.g. 15 B compliance) and if applicable additional equipment authorizations (e.g. SDoC) of the host product to be addressed by the integrator/manufacturer.

This module is only FCC authorized for the specific rule parts 15.247, 15.407 listed on the grant, and the host product manufacturer is responsible for compliance to any other FCC rules that apply to the host product as being Part 15 Subpart B compliant.

Flairmesh Technologies -27-